Dans un article précédent j'ai expliqué comment fonctionne l'unitée arithmétique et logique d'un microcontrôleur. Dans cette article j'explique comment fonctionne le décodeur d'instruction. On va prendre pour exemple le coeur PIC baseline.

Voici le cycle d'instruction d'un coeur baseline.

Il faut 4 cycles d'oscillateur pour exécuter une instruction. Ces cycles sont appelés Q1,Q2,Q3,Q4 sur le diagramme ci-haut. Il s'agit d'un automate fini(state machine) qui fait évoluer l'exécution d'une étape à l'autre. Ce qui se passe dans un état Qx donné dépend en partie de l'instruction qui est exécutée mais certaines étapes sont communes à toutes les instructions. Sans connaître l'implémentation réelle du MCU on va essayer de comprendre son fonctionnement. On réalise qu'au démarrage le fetch register ou pileline est vide, il faut donc que le premier cycle d'instruction exécute un NOP. cette instruction a le code 0, donc lors d'une réinitialisation le fetch register doit-être mis à zéro. Au démarrage le compteur ordinal contient la valeur de la dernière adresse flash. Celle-ci contient une instruction MOVLW qui transfert dans W le valeur de calibration du registre OSCCAL. Au deuxième cycle, au début de l'exécution de cette instruction le compteur ordinal retombe à zéro et l'instruction qui est à l'adresse zéro est transférée dans le fetch register.On va prendre en exemple 2 instructions, GOTO et ADDWF. Commençons par le GOTO. Le code opérationnel de cette instruction est encodée sur les 3 bits les plus significatifs (les instructions sont encodées sur 12 bits) et correspond à 101. Voici comment elle pourrait-être décodée.

Ce schéma est partiel, je n'ai pas dessiner tous les bus et les portes de sélection (tristate gate). C'est en utilisant ces portes de sélection que les informations sont transférées d'un registre à l'autre par les différents signaux Qx. Comme on le voit sur le schéma ci-haut. Les signaux Qx sont décalés dans le temps les uns par rapport aux autres de sortent qu'ils agissent l'un après l'autre. Ce sont eux qui permettent de passer d'une étape à la suivante. Voiçi les étapes pour le GOTO, les étapes 1 à 3 sont communes à toutes les instructions:- Sur la transition Q1 montante on peut transférer le contenu du registre fetch register dans le registre décodeur d'instruction (instructon register). En même temps le contenu du compteur ordinal peut-être transféré vers une des entrée de l'UAL et la valeur 1 sur l'autre entrée.

- Sur la transition descendante de Q1 le contenu du bus data de la mémoire programme peut-être transféré dans le fetch register.

- Sur la transition montante de Q2 le résultat de l'incrément dans l'UAL est renvoyé dans le compteur ordinal.

- Sur Q2 descendant on peut transférer les 9 bits faibles de l'instruction register qui contienne l'adresse de destination du GOTO vers le compteur ordinal.

- A cause du changement de valeur du compteur ordinal, le contenu du fetch register n'est plus valide. On doit le remplacer par une instruction NOP de sorte qu'au cycle suivant le fetch register sera rempli avec l'instruction pointée par la nouvelle adresse du compteur ordinal. Voilà pourquoi les instructions de saut prennent 2 Tcy au lieu d'un seul. Cette opération peut-être effectuée pendant les phases Q3 et Q4.

Le compteur ordinal a plus de 8 bits alors que ce passe-t-il lors de l'incrément lorsqu'il y a débordement? A mon avis la façon la plus simple de régler ce problème est en fait d'avoir un UAL qui a autant de bits que le compteur ordinal. Même si l'UAL est plus large que le bus de données ça ne pose pas de problème et pour une petite UAL comme celle-ci le coup supplémentaire est sans doute négligeable.

ADDWF

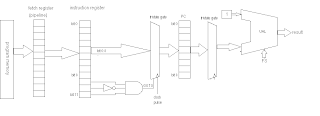

Voici un schéma partiel d'un décodeur pour cette instruction.

Comme W est utilisé comme opérande on envoie son contenu à une des entrées de l'UAL. Les 5 bits les plus faibles de l'instruction sélectionne l'autre entrée à partir du register file. Ça peut-être une location RAM ou un SFR. S'il le register file a plus que 32 locations, il y a un bank select register qui est utilisé pour adresser les bits les plus forts de l'adresse ou bank. Si la mémoire de PIC baseline est fragmenté en segments c'est justement parce que dans l'instruction il n'y a que 5 bits pour addresser le register file. L'adressage doit donc être complété par le registre BSR (Bank Select Register).

Notez comment le bit d de l'instruction est utilisé pour sélectionner la destination du résultat. Si d vaut zéro c'est la porte qui conduit vers W qui est ouverte. Par contre si d vaut un, c'est la porte qui conduit vers le register file qui est ouverte. Un petit rond à l'entrée de contrôle d'une porte signifie que le signal est inversé (active low).

décodeur ROM

Créer un décodeur pour chaque instruction peut nécessité beaucoup de portes logiques même si les instructions peuvent partager des portes, par exemples les inverseurs sont communs à tous les décodeurs. Il y a une autre façon de procéder, il s'agit d'utiliser un décodeur ROM (Read Only Memory). Les bits data de la ROM sont fabriqués avec un masque métallique plutôt que des portes et ont un faible coût. L'idée est simple à implanter, les bits de l'instruction register qui contiennent le code opérationnel sont utilisés comme adresse d'une mémoire ROM. Les lignes de sortie de donnée de la ROM sont utilisés comme signaux pour contrôler les portes, en plus certaines lignes de données sont retournées vers le bus d'adresse de la ROM ce qui permet de faire évoluer l'automate de manière simple d'une étape à l'autre.

Supposons que le opcode est 5 et que les bits à la sortie du latch sont toujours à zéro au début du cycle d'instruction. À l'adresse 5 de la mémoire ROM on met les bits data aux valeurs qu'on a besoin sur le bus de contrôle et on envoie dans le latch les bits qui combinés avec les bits qui proviennent de l'instruction register vont donner l'adresse en ROM qui contient les valeurs de bits qu'on aura besoin à la prochaine étape du décodage. Ce genre de state machine est fréquemment utilisé, particulièrement dans les FPGA.